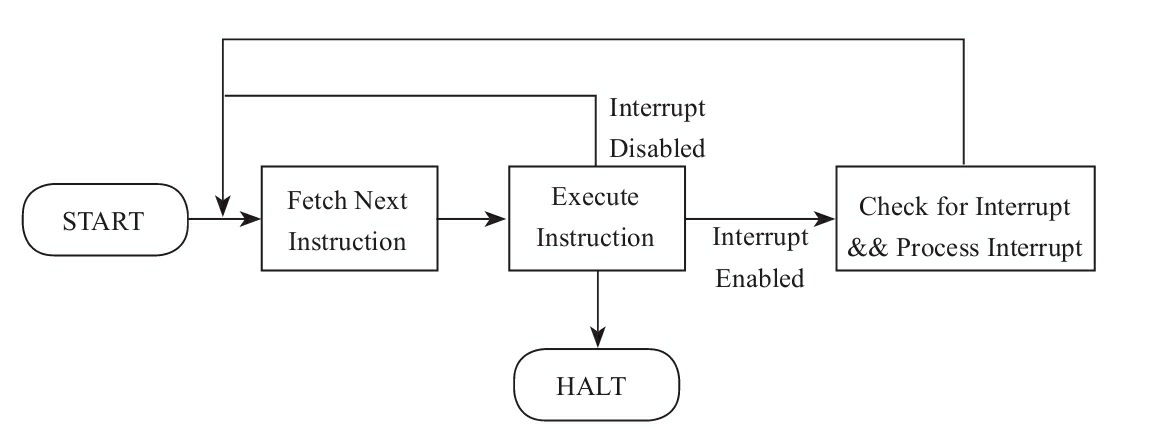

当操作系统允许CPU响应中断后,每当执行完一条指令,CPU都将检查中断引脚是否有效,一旦有效,CPU将处理中断,之后回来再继续执行下一条指令。

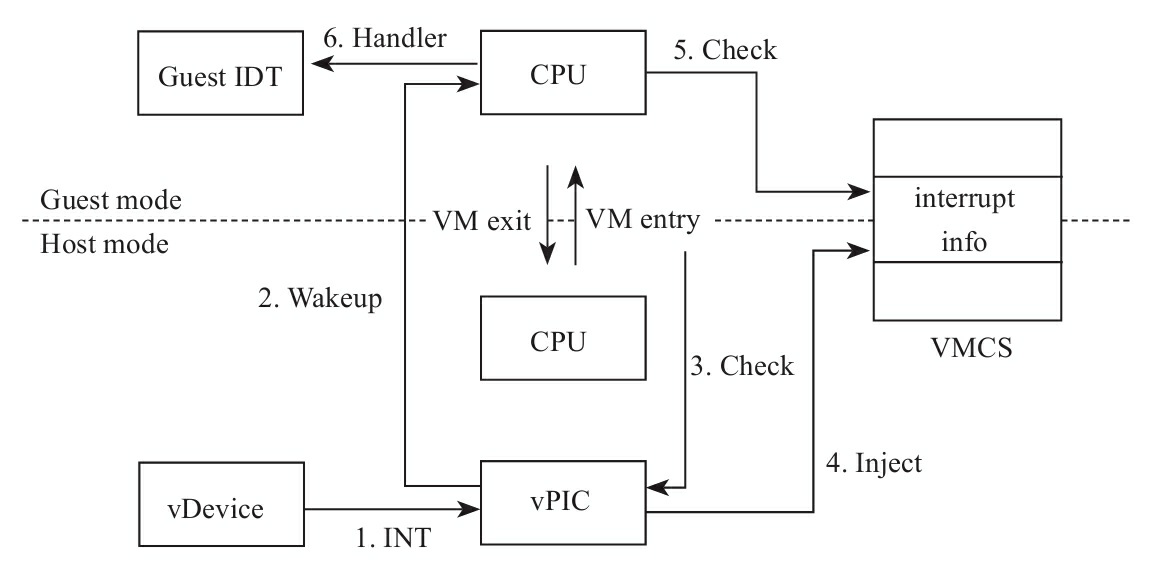

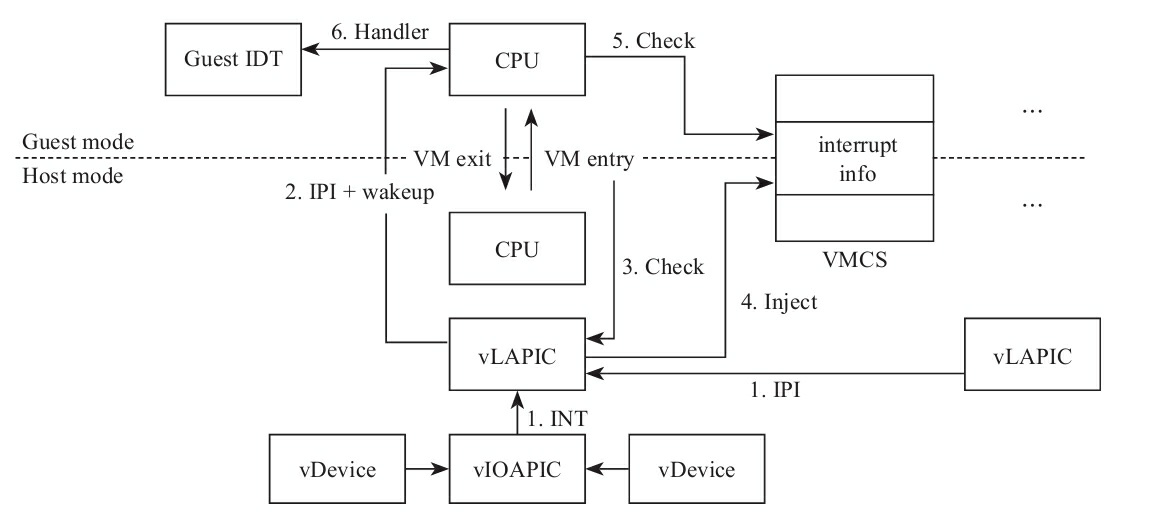

早期的CPU是有物理连接到中断控制器,中断控制器连接到CPU的INTR引脚,通过电平来告知CPU需要处理中断,CPU会主动检查INTR引脚来确定是否中断。虚拟中断原理相同,对于”虚拟中断“控制器来说,该引脚是一个变量,设置该变量的值,就可以理解为中断芯片有中断请求了。

KVM发现虚拟中断有中断请求时,会向VMCS中VM-entry control部分的VM-entry interruption-information field字段写入中断信息,在切入Guest模式的时候,CPU检查VMCS这个字段,就如同检查CPU的引脚,如果有中断,则进入中断的执行流程。

Guest模式的CPU和虚拟中断处于两个不同的”世界“,Guest模式的CPU不能够检查虚拟中断芯片引脚,只能在VM-entry时候由KVM代为检查,然后写入VMCS中。所以对于Guest,如果需要中断的注入,那么就需要先VM exit再写入VMCS再回Guest进行处理。

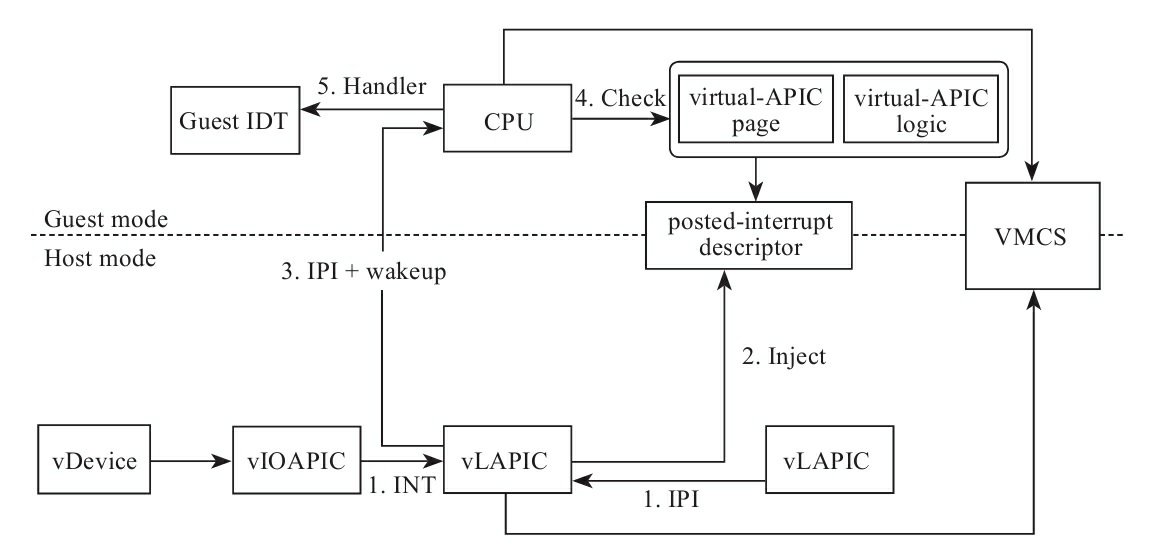

(物理LAPIC设备上一个页面大小的内存用于存储寄存器,APIC Page)Intel在硬件层面对中断虚拟化进行了支持。

- 实现了一个处于Guest模式的APIC页面,称为virtual-APIC page。

- 在Guest模式实现了部分中断芯片逻辑(虚拟中断逻辑),这样在Guest模式下就有了状态和逻辑,就可以模拟很多中断的行为(访问中断寄存器、跟踪中断的状态、向CPU递交中断),这个操作就导致了很多中断不需要VMM介入。但是有些中断还是无法避免需要切换到VMM中(比如通过写ICR寄存器发送IPI,会触发VM exit,由本地LAPIC向目标LAPIC发送IPI)。

在此硬件虚拟化的机制支持下,LAPIC收到中断,主动向处于Guest模式的CPU通知(LAPIC将中断写入posted-interrupt descriptor->LAPIC通过特殊的核间中断posted-interrupt notification通知目标CPU->目标CPU在Guest模式下借助中断逻辑处理中断)。

参考文献

- 《深度探索Linux系统虚拟化:原理与实现》 - 王柏生 & 谢广军

评论区